# ANNUAL2021 REPORT2021

Instituto de Microelectrónica de Sevilla

# OUTLINE

# FOREWOR ..... ABOUT IMSE ..... Organization ..... Human Resources Budget ..... Infrastructure ..... RESEARCH AREAS & LINES Analog signal processing..... • Digital signal processing & vlsi systems ..... Brain-inspired neural networks and artific Sensory & photonic vision systems..... Nanoelectronics and emerging technolog Biomedical and bioinspired circuits and sy Integrated circuits for space applications Hardware security..... FUNDED PROJECTS.....

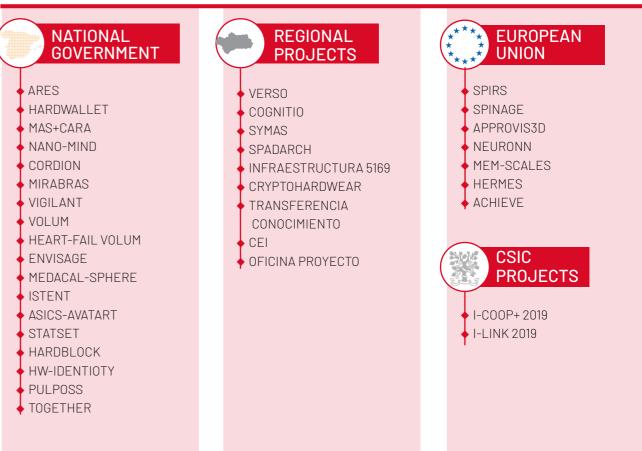

- National project .....

- Regional project.....

- EU project .....

- CSIC project.....

# PUBLICATIONS .....

- Books .....

- Journal Papers .....

- Conference Papers .....

# THESIS.....

# TECHNOLOGICAL TRANSFER .....

- New Patent .....

- EXTERNAL LIAISON .....

- AWARDS & RECOGNITION .....

- OUTREACH.....

- SOCIAL MEDIA ..

Instituto de Microelectrónica de Sevilla

#### INSTITUTO DE MICROELECTRÓNICA DE SEVILLA Centro Nacional de Microelectrónica

C/ Américo Vespucio (Intersection with Leonardo Da Vinci) PCT Cartuja: 41092 - Seville, Spain

Phone: +34 95 446 66 66 Fax: +34 95 446 66 00

www.imse-cnm.csic.es

Layour and design: tiporium.com

| 9                                                                    |

|----------------------------------------------------------------------|

|                                                                      |

|                                                                      |

| 24                                                                   |

| cial intelligence                                                    |

|                                                                      |

| ies                                                                  |

| vstems                                                               |

| 41                                                                   |

|                                                                      |

|                                                                      |

|                                                                      |

| ( -                                                                  |

|                                                                      |

|                                                                      |

|                                                                      |

|                                                                      |

|                                                                      |

|                                                                      |

| 57<br>                                                               |

| 57<br>61<br>64<br>66<br>66                                           |

| 57<br>61<br>64<br>66<br>66<br>67                                     |

| 57<br>61<br>64<br>66<br>66<br>66<br>71                               |

| 57<br>61<br>64<br>66<br>66<br>67<br>71<br>74                         |

| 57<br>61<br>64<br>66<br>66<br>67<br>71<br>74<br>75                   |

| 57<br>61<br>64<br>66<br>66<br>67<br>71<br>71<br>74<br>75<br>75       |

| 57<br>61<br>64<br>66<br>66<br>67<br>71<br>71<br>74<br>75<br>75<br>75 |

# FOREWORD

This report summarizes the research activities and the main achieved objectives by the Instituto de Microelectrónica de Sevilla (IMSE) during 2021. This period was marked by slow and progressive recovery from the pandemic. Coronavirus vaccines started to become available and people could slowly return to be physically present at the Institute. After the summer of 2021, CSIC gave instructions to return to full presence, except for special health related cases.

During 2021 the institute had three industrial contracts running, and was granted or initiated one IMSE-coordinated EU project, four national projects, five regional projects, three University of Sevilla projects, one infrastructure project, and nine young employment grants, all totaling 3.6 million euros. Our researchers published 47 international journal papers and filed 2 patents. A total of 3 Ph.D. theses were defended. As a consequence of all this, the Institute reached 100% of the targets set in the CSIC Strategic Plan, particularized with the indicators collected in the PC0 (Productivity of Achievement of Objectives).

Overall, 2021 was a good year, with good productivity, as personnel begun to recover from the hit of the pandemic.

The Instituto de Microelectrónica de Sevilla (IM-SE-CNM - Seville Institute of Microelectronics) is an R&D&I joint center of the Consejo Superior de Investigaciones Científicas (CSIC - Spanish National Research Council) and the Universidad de Sevilla. Together with its counterpart institutes in Barcelona and Madrid, it forms part of the Centro Nacional de Microelectrónica (CNM - National Microelectronics Center).

The Institute is dedicated to the field of Physical Science and Technologies, one of the eight areas into which research activity is divided by the CSIC. Its main area of specialization is the design of CMOS analog and mixed-signal integrated circuits and their use in different application contexts such as radiofrequency, microsystems or data conversion.

The IMSE-CNM began its operations in October 1989 under the auspices of an agreement signed by the Junta de Andalucía (the Andalusian Regional Government), the CSIC and the Universidad de Sevilla. Its founding research group was initially based on the premises of the Centro de Informática Científi-

> ca de Andalucía (CICA - Scientific Computing Center of Andalucía), as a subsidiary department of the Instituto de Microelectrónica de Barcelona (Barcelona Institute of Microelectronics). Later, in 1996, it was

# **DIRECTIONS:**

The Instituto de Microelectrónica de Sevilla (IMSE) is located in the Parque Científico y Park) on Isla de La Cartuja, at the corner of Calle Américo Vespucio and Calle Leonardo da Vinci.

— C/ Américo Vespucio, 28. Parque Científico

- + 34 954 466 666

- www.imse-cnm.csic.es

- info@imse-cnm.csic.es

- GPS: 37° 24′ 44″ N 06° 00′ 21″ W.

established by the Governing Board of the CSIC as a Institute in Formation, occupying a building next to the CICA ceded by the Junta de Andalucía. In late 2008, the Institute was enlarged and relocated in new premises purpose-built by the CSIC in the Parque Científico y Tecnológico Cartuja (Cartuja Scientific and Technological Park). On October 2015, by means of a Specific Collaboration Agreement signed by the CSIC and the Universidad de Sevilla, the center became a Joint Institute of both institutions.

The IMSE-CNM staff consists of approximately one hundred people, including scientists and support personnel. Most of them work for the CSIC and the Universidad de Sevilla. IMSE-CNM employees are involved in advancing scientific knowledge, designing high level scientific-technical solutions and in technology transfer. Their duties include both research and teaching activities, the latter mainly at official master and PhD degrees.

The projects undertaken at the Institute mostly correspond to EU research initiatives, National R+D Plans and Research Plans funded by the Junta de Andalucía. They focus primarily on implementing innovative concepts in silicon, using either the CNM's own clean room at the Instituto de Microelectrónica de Barcelona (IMB-CNM) or external foundries, mainly from Europractice or CMP IC services.

The Institute also participates in several technology and knowledge transfer activities with microelectronics companies, at both national and international level. These activities take the form of collaboration in numerous research contracts, the organization of training courses and the provision of scientific and technical consultation services for companies and government departments.

The Instituto de Microelectrónica de Sevilla (IMSE-CNM) is a joint center of the Consejo Superior de Investigaciones Científicas (CSIC - Spanish National Research Council) and the Universidad de Sevilla.

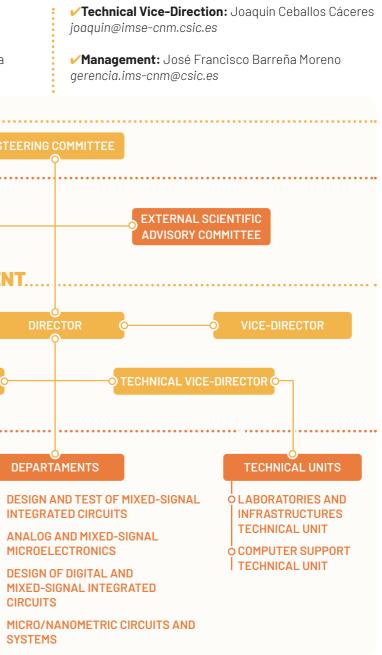

The IMSE-CNM management structure is as follows:

- ✓ **Direction:** Bernabé Linares Barranco direccion.ims-cnm@csic.es

- ✓Vice-Direction: José Manuel de la Rosa Utrera jrosa@imse-cnm.csic.es

# ... GOVERNING..... ADVISORY. SCIENTIFIC BOARD DIRECTION AND MANAGEMENT. **GOVERNING BOARD** ... OPERATIONAL MANAGEMENT SERVICES DEPARTAMENTS SERVICES CIRCUITS SYSTEMS

#### ADMINISTRATIVE SERVICES UNIT

The Institute's research activities are carried out by Research Units responsible for project development. There are currently four of these units:

- Design and Test of Mixed-Signal Integrated Circuits

- Analog and Mixed-Signal Microelectronics

- Design of Digital and Mixed-Signal Integrated Circuits

**6** | ABOUT IMSE

- Micro/Nanometric Circuits and Systems

- The Institute's infrastructure is also supported by two Technical Units.

- Laboratories and Infrastructures Technical Unit

- Computer Support Technical Unit

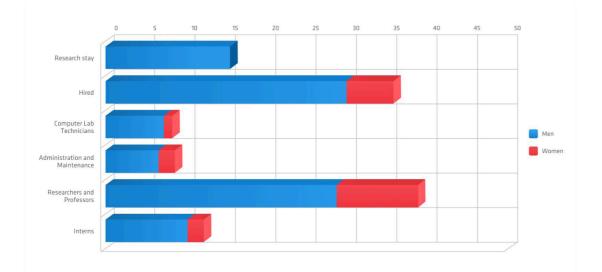

# **HUMAN RESOURCES**

The personnel at the IMSE-CNM permanently or temporarily engaged in the Institute's activities includes nearly 110 people. Most of them work for the CSIC and the Universidad de Sevilla, but there are also teachers and students from other organisms on research internships as it is shown in the figure. These internships do not imply any kind of em ployer-employee relationship with the CSIC

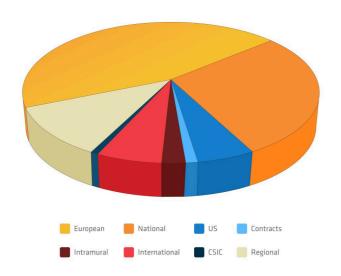

# BUDGET

Incoming resources, distributed by concepts, for the year 2021 are shown in the following graphs (excluding staff costs). External funding is obtained either from competitive public projects or industrial contracts. Operating expen ses are provided by CSIC and Universidad de Sevilla.

# **INFRASTRUCTURE**

# LABORATORIES

IMSE-CNM has its own laboratories and workshops, specifically habilitated for research, development and innovation tasks carried out at the Institute. The laboratories are well fitted out with equipment and instrumentation, and are run by a permanently employed team of specialists.

#### Head of Unit

Joaquín Ceballos Cáceres joaquin@imse-cnm.csic.es >

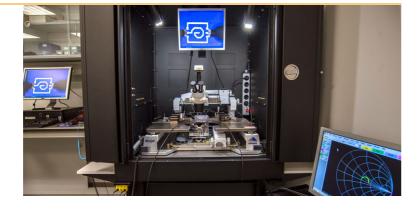

# **DEVICE CHARACTERIZATION LAB**

This laboratory is mainly dedicated to perform parametric measurements in semiconductors and passive devices. In this lab it is possible to acquire internal signals from the semiconductors, already cutted and packaged, or from wafers up to 3.5", and performing tests at temperatures ranging from -125°C to 150ºC.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

#### Equipment

Semiconductor Parameter Analyzers, Climatic Chambers, Probe Station, Temperature Forcing System, C Meter CV Plotter, LCR Meter.

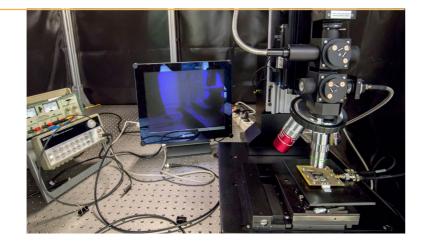

# **OPTOELECTRONICS LAB**

This lab is equipped with the instrumentation needed to characterize visible light sensors and integrated circuits made up of discrete sensors or visible light matrices. A dark chamber is also available for sensor characterization.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

Equipment Optical Characterization Equipment, Monochromator, Pulsed Laser, Video Development Platform, Lux Meter, Laser Modules, Photo and Video Lenses, Spectrometer

### **RADIOFREQUENCY LAB**

It allows to perform spectrum and network measurements, and it is equipped with an anechoic chamber for device characterization or electromagnetic compatibility (EMC) measurements. It also allows to perform on wafer (up to 150 mm) as well as on printed circuit measurements.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

### Equipment

Anechoic Chamber, Noise Figure Analyzer, Spectrum/Network Analyzers, Probe Station, Vector Signal Generators, Noise Sources, Power Meter

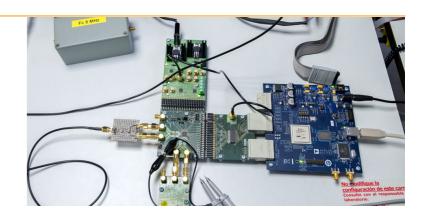

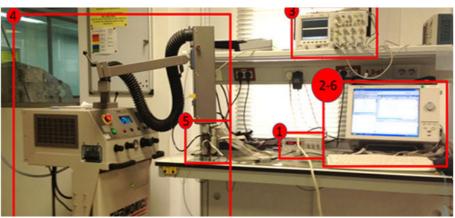

### **A/D MEASUREMENT LAB**

This is the largest lab in the IMSE. It has twelve fully-reconfigurable mobile stations to carry out the experimental tests on mixed-signal integrated circuits. It also has twelve carts with spectfic measurement equipment that can be attached to any of the mobile stations depending on the requirements of the A/D measurements to perform.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

#### Equipment

Spectrum/Network Analyzers, Logic Analyzers, Arbitrary Waveform Generators, Pulse Generators, Oscilloscopes, Data Acquisition Boards, Differential Amplifiers, Frecuency Counters, Switch/Control Unit, Test Systems, Power Meter, Electrometer, Lock-in Amplifier, Picoammeter, Phase Noise Measurement System.

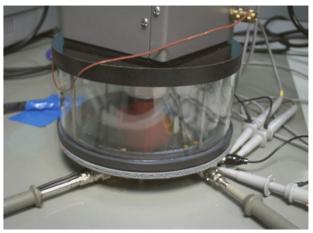

This lab is equipped with the new pulsed laser PULBOX PICO-RAD compact system for single-event effects testing. Using a single photon technique and a 1064nm wavelength (near-infrared) pulsed laser source, this facility allows the study of the impact of high energy particles over integrated circuits for space, medical or nuclear applications.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

Equipment Pulsed Laser, Oscilloscope

# **CIBERSECURITY LAB**

The Cibersecurity Laboratory has the required equipment to evaluate the immunity against different types of collateral channel attacks, which are based on the information obtained from the physical implementation of the cryptosystems (power consumption, algorithm's execution time, response to induced failures, electromagnetic emission, etc.).

Antonio Ragel Morales ragel@imse-cnm.csic.es

Equipment

## **COMPLEX SYSTEMS LAB**

This lab has been designed to provide accommodation to those systems that, due to either their size or their special characteristics, require a greater space or an isolated environment. It is also equipped with a showcase for the manipulation of dangerous chemical products and a security cabinet.

#### **Chief Lab Technician**

Antonio Ragel Morales ragel@imse-cnm.csic.es

# Equipment

### **ATE AGILENT 93000**

The Agilent 93000 SOC C200e Semiconductor Test System allows carrying out prototyping and fabrication tests of mixed-signal circuits (either already packaged or directly onto the wafer) in one only platform. It is also possible to incorporate the Thermonics T-2650 BV, a temperature forcing system that allows to perform the tests under temperature conditions ranging from -55ºC to 200ºC.

#### **Chief Lab Technician**

José M. Mora Gutiérrez jmiguel@imse-cnm.csic.es

Equipment System, Oscilloscope

Device Current Waveform Analyzer, Logic Analyzers, Function Generators, Pulse Generators, Oscilloscopes, Arbitrary Waveform Generator, Power Meter, Motorized XY Microscope Stage, Ultra Wide Band Low Noise Amplifier, Data Acquisition System, Power Supply

Koala Robot, Area Preparation System, 3D Printer

Agilent 93000 Semiconductor Test System, Temperature Forcing

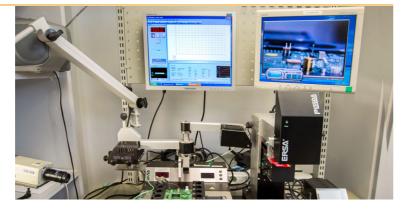

### SPECIAL ASSEMBLY WORKSHOP

The Special Assembly Workshop has equipment for soldering and desoldering high density packaging components, such as BGAs, mini-BGAs and fine-pitch surface-mount components

#### **Chief Lab Technician**

Miguel A. Lagos Florido mlagos@imse-cnm.csic.es

Equipment

IR Rework System, Precision Placement System, Soldering Stations

# **PACKAGING WORKSHOP**

This workshop is devoted to make the bonding between chip and package. It has all the required resources to face the challenges that deep-submicron technologies pose, allowing connections with pitch sizes down to 50 µm. This workshop features two semi-automatic ultrasound micro-soldering machines, with thread diameters of up to  $17 \,\mu m_{e}$ for ball-bonding and wedge-bonding. To verify the quality of connections, there is a micro-soldering test system for evaluating thread-resistance and solder ball shear. It also has two chip and wafer storage units for keeping ICs at optimal temperature and humidity conditions.

Chief Lab Technician Manuel Repiso repiso@imse-cnm.csic.es

### PCB ASSEMBLY WORKSHOP

The PCB Assembly Workshop has all the equipment needed for soldering and desoldering thru-hole circuits mounted on PCBs, perforated matrix plates, and, in general, on any circuit-test development plates that do not require special welding techniques.

Chief Lab Technician

Manuel Repiso repiso@imse-cnm.csic.es

Equipment

Wire Bonders, Bondtester, Ultra Low Humidity Cabinets

Equipment Soldering & Desoldering Stations, Ultrasonic Cleaning Bath

# CAD TOOLS

Most of the software tools used at the IMSE-CNM are design tools which cover several stages of the integrated circuit design process, from automatic HDL-based synthesis to the completion of full-custom layouts. As a member of the European consortium EUROPRACTICE, IMSE-CNM holds many of the licenses required by these design tools. The CAD software tool library at IMSE-CNM also includes in-house CAD tools and free-distribution tools from universities and other research centers.

CAD Manager

Dolores Vázquez Boza Iola@imse-cnm.csic.es

# **COMMERCIAL TOOLS**

## **CADENCE DESIGN FRAMEWORK II**

#### Analog and digital semi/full-custom design.

Cadence provides a complete integrated circuit environment allowing both analog design flows (schematic capture, electrical simulation, layout editing, design rule checking, parasitic extraction, LVS verification, etc.) and digital flows (functional description, automatic synthesis, logic simulation, automatic place & route, etc.). The environment also includes tools and languages for describing and simulating mixed analog-digital designs (AHDL, hierarchy editor, etc.).

### **MENTOR GRAPHICS**

#### Analog and digital semi/full-custom design.

Mentor Graphics provides a complete integrated circuit environment allowing full digital design flow (functional description, automatic synthesis, logic simulation). This tool also covers semi-custom and full-custom layout design.

# **SYNOPSYS**

#### Simulation and VHDL synthesis.

Synopsys provides a series of HDL simulation and synthesis tools (VHDL and Verilog) for designs in both ASIC and FPGA technologies. The current distribution of this tool includes also packages for high-level synthesis, low-power synthesis, design for testability, test files and test vector generation, formal verification, temporal analysis and the use and development of IP modules.

# XILINX

#### FPGAs development.

Xilinx provides different tools for FPGA system design: Integrated Software Environment (ISE), a basic set of tools that facilitates the description, synthesis, implementation and verification of designs created on Xilinx CPLDs and FPGAs; Embedded Development Kit (EDK) for programmable embedded system design; ChipScope Pro, which makes it possible to

display all the signals and internal nodes of an FPGA; and System Generator for DSP, for developing digital signal processing systems on FPGAs.

# SABER

#### Electrical simulator for mixed-signal designs.

Among other utilities, this includes: SaberHDL, a tool for simulating complex mixed-signal systems or technologies; SaberDesigner, for creating and editing designs, controlling simulations interactively and displaying and analyzing waveforms; SaberGuide, for behavioral simulation; SaberSketch, a graphical user interface; and MAST, a mixed-signal hardware description language.

### HSPICE

#### Electrical simulator.

The standard tool for simulating circuits at electrical level, this simulator makes it possible to incorporate certified device models from leading MOS device manufacturers. Featuring latest-generation simulation and analysis algorithms, it has become one of the most reliable and best known industrial circuit simulators.

### **IN-HOUSE CAD TOOLS**

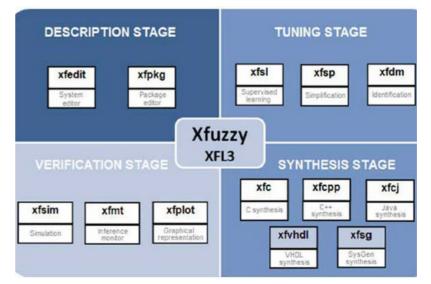

## XFUZZY

#### **Design of fuzzy-inference systems**

Xfuzzy, the design environment for fuzzy systems, includes a set of tools that help with the design of fuzzy-logic inference-based systems, from initial description right through to final implementation. Based on the XFL specification language, Xfuzzy has tools for describing, verifying and synthesizing fuzzy systems (both software and hardware). It also features tools which allow the easy editing of package operators and hierarchical structures, tools for generating 2-D and 3-D data graphics and tools for monitoring inference processes.

## FRIDGE

#### **Circuit optimization using simulated annealing** techniques

FRIDGE is an analog circuit optimization tool with many innovative features. It was developed to streamline the process of designing integrated circuits. FRIDGE is used to size analog circuits automatically according to design requirements. The

## AGILENT ADVANCED DESIGN SYSTEM

#### Design tool for high frequency design.

The Advanced Design System (ADS) is an electronic design automation tool for RF, microwave and signal integrity applications. It uses cutting edge technologies such as 3D EM and X-parameter simulators. This tool is used by leading developers of wireless applications for communications and networks, and also by leading aerospace and defense technology companies. In one single integrated platform ADS provides design and verification standards, with wireless design libraries and EM circuit-system co-simulation, for WiMAX, LTE, multi-gigabit links and radar and satellite communications applications.

## MATLAB/SIMULINK

High-level technical computing language and interactive prototype design and development. Dynamic and embedded multi-domain simulation environment. MATLAB is a high-level technical computing language and an interactive platform for algorithm design, numerical computation and data analysis and visualization. Simulink is a tool for multi-domain simulation and design based on dynamic and embedded system models.

optimization process takes place in two stages: in the first, statistical optimization techniques are applied, while deterministic techniques are applied in the second. Computational costs are drastically reduced by correctly formulating the cost function (where the designer's requirements are established) and adjusting the movement generator to match the nature of the analog sizing problem. All this can be done thanks to FRIDGE's innovative features, which include: preliminary exploration of the design space using a coarse grid to determine the best regions for further exploration, adaptive control of the temperature in the simulated annealing statistical techniques, synchronization of movement amplitude in parameter space with the temperature, etc.

# SIMSIDES

#### SIMulink-based Sloma-DElta Simulator

SIMSIDES is a time-domain behavioral simulator for  $\Sigma \Delta Ms$  that was developed as a toolbox in the MAT-LAB/SIMULINK environment. SIMSIDES can be used for simulating any arbitrary  $\sum \Delta M$  architecture implemented with discrete-time (DT) or continuous-time (CT) circuit techniques.

# **RESEARCH AREAS & LINES**

The Instituto de Microelectrónica de Sevilla is structured into Research Units whose scientific objectives focus primarily on the implementation and experimental verification of innovative concepts related to the design of microand nano-electronic circuits and systems.

The Research Lines developed at IMSE-CNM aim to provide solutions both in traditional sectors, such as communications, processing systems or instrumentation, and in emerging sectors, such as medical engineering, environment or space technology. These lines also consider the introduction of new devices, such as nano-sensors and micro-electro-mechanical systems (MEMS), and the use of unconventional computing paradigms, such as neural networks or fuzzy logic.

# **RESEARCH AREAS**

#### ANALOG SIGNAL PROCESSING

- Analog, Mixed-Signal and Radio Frequency (AMS-RF) Circuits

- Analog-to-Digital Converters and Mixed-Signal Interfaces

- T est and Design-for-Test of Analog, Mixed-Signals and RF (AMS-RF) Circuits

- Systems

- Low-Voltage and Low-Power Analog and Mixed-Signal Design in Deep Submicron and Nanometer CMOS Technologies

- Sigma-Delta Data Converters

#### **DIGITAL SIGNAL PROCESSING & VLSI SYSTEMS**

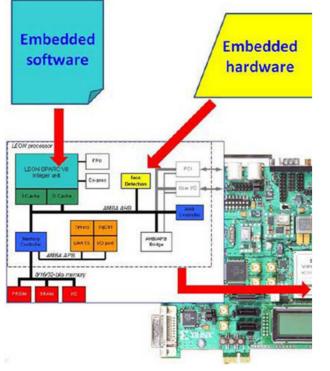

- CMOS Digital Intelligent and Suistainable Integrated Circuits

- DigItal Embedded Systems and IoT

- Cybersecurity

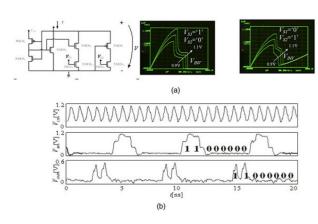

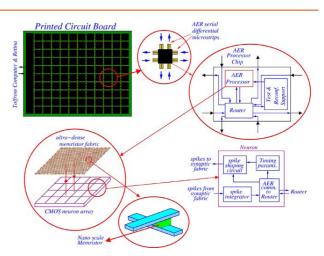

#### BRAIN-INSPIRED NEURAL NETWORKS AND ARTIFICIAL INTELLIGENCE

- Neuromorphic Cognitive Systems

- Microelectronic Systems for Computational Intelligence

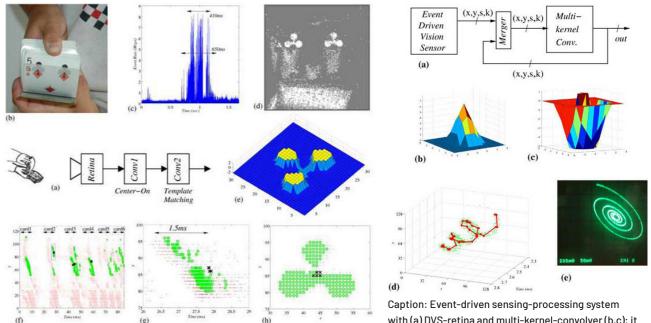

#### **SENSORY & PHOTON IC VISION SYSTEMS**

- CMOS Smart Imagers and Vision Chips

- Heterogeneous Sensory-Processing Systems and 3-D

- Integration

- Dynamic Vision Sensors

#### NANOELECTRONICS AND EMERGING TECHNOLOGIES

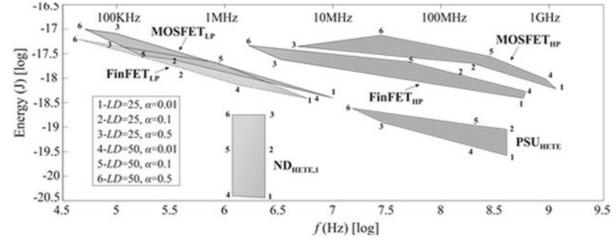

- Circuit Design using Emerging Devices and Non-Conventional Logic Concepts

- Nanoscale Memristor Circuits and Systems

#### **BIOMEDICAL AND BIOINSPIRED CIRCUITS** AND SYSTEMS

- **Biomedical Circuits and Systems**

- Wireless Implantable and Wearable Intelligent Biosensor Devices

#### INTEGRATED CIRCUITS FOR SPACE APPLICATIONS

High-Speed High-Resolution ADCs & DACs for Space

Modeling, Design and Synthesis Techniques of Analog, Mixed-Signal, RF and Heterogeneous Circuits and

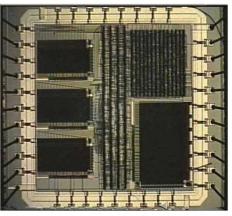

# RESEARCH AREA ANALOG SIGNAL PROCESSING

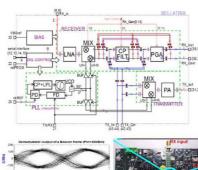

Analog, Mixed-Signal and Radio Frequency (AMS-RF) Circuits

#### Contact

Eduardo Peralías Macías

peralias@imse-cnm.csic.es

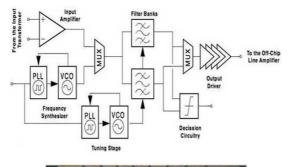

The activities of this research line focus on the development of design techniques and methodologies, mainly in advanced CMOS technologies, for analogue mixed-signal and radiofrequency circuits, with special emphasis on analogue-digital converters (ADCs) and application specific IPs (intellectual properties) for front-end analogue signal processing applications that require low power consumption, high speed and high resolution. We develop concepts such as robustness against technological variability and environmental conditions, digital calibration, self-correction and self-adjustment. All this in the framework of systems for different applications, and specifically for aerospace and wireless communications applications.

#### Kevwords

Analog Design; Analog-to-Digital Converters; Radio Frequency Front-End; Digital Calibration; Self-Correction; Wireless and Space Applications

#### **Research Highlights**

• J.L. Gonzalez, J.C. Cruz, R.L. Moreno and D. Vazguez, "A Proposal for Yield Improvement with Power Tradeoffs in CMOS LNAs", IEEE Latin America Transactions, vol. 14, no. 1, pp. 13-19, Jan 2016 »

R. Fiorelli and E. Peralías, "Semi-empirical RF MOST model for CMOS 65nm technologies: Theory, extraction method and validation", Integration, the VLSI Journal, vol. 52, pp. 228-236, 2016»

◆ A. Ginés, R. Fiorelli, A. Villegas, R. Doldán, M. Barragán, D. Vázquez, A. Rueda and E. Peralías, "Design of an Energy Efficient ZigBee Transceiver", Chap. 7 in Thomas Noulis (Ed.), Mixed-signal circuits, CRC-Press, 2015 »

◆ A.J. Ginés, G. Leger, E. Peralías and A. Rueda, "Close-loop Simulation Method for Evaluation of Static Offset in Discrete-Time Comparators", Proceeding of the IEEE International Conference on Electronics Circuits and Systems (ICECS), Marsella, 2014 »

• R. Fiorelli, F. Silveira and E. Peralias, "MOST Moderate-Weak-Inversion Region as the Optimum Design Zone for CMOS 2.4-GHz CS-LNAs", IEEE Transactions on Microwave Theory and Techniques, vol. 62, no. 3, pp. 556-566, 2014 »

#### Key Research Projects & Contracts

n-PATETIC: New paradigms for testing mixed-signal integrated circuits (TEC2015-68448-R) PI: Adoración Rueda Rueda Funding Body: Min. de Economía y Competitividad Jan 2016 - Dec 2018

#### DANTE: Adapting Mixed-signal and RF ICs Design and Test

to Process and Evironment Variability (TEC2011-28302) PI: Adoración Rueda Rueda Funding Body: Min. de Ciencia e Innovación Jan 2012 - Dec 2015

#### ACATEX: Self-calibration and self-test of analog, mixed-signal and radio frecuency circuits (P09-TIC-5386) PI: Adoración Rueda Rueda

Funding Body: Junta de Andalucía - Proyectos de Excelencia

Mar 2010 - Feb 2014

#### SR2: Short Range Radio (2A105- Catrene) (TSI-020400-2008-71 and TSI-020400-2010-55) » web

PI: Adoración Rueda Rueda Funding Body: Catrene European Program y MITyC Programa Avanza+

Jan 2008 - Dec 2011

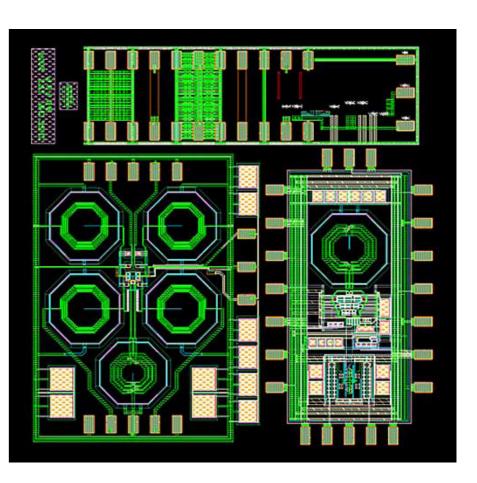

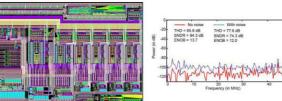

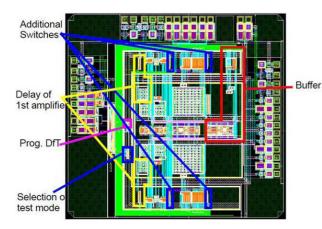

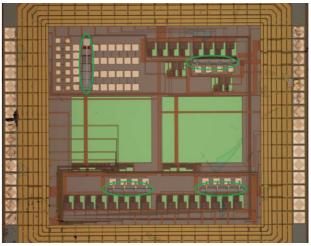

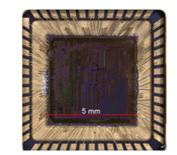

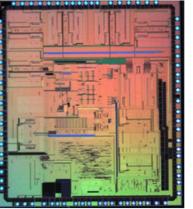

Caption: 1.8V 15-bit 100Msps Pipeline ADC: layout and post-layout simulation results of Nyquist performance with and without transient noise

Caption: Prototype of a Zigbee/ IFFF 802.15.4 transciever, implemented in a 1.2V 90nm CMOS technoloav

### **Analog-to-Digital Converters** and Mixed-Signal Interfaces

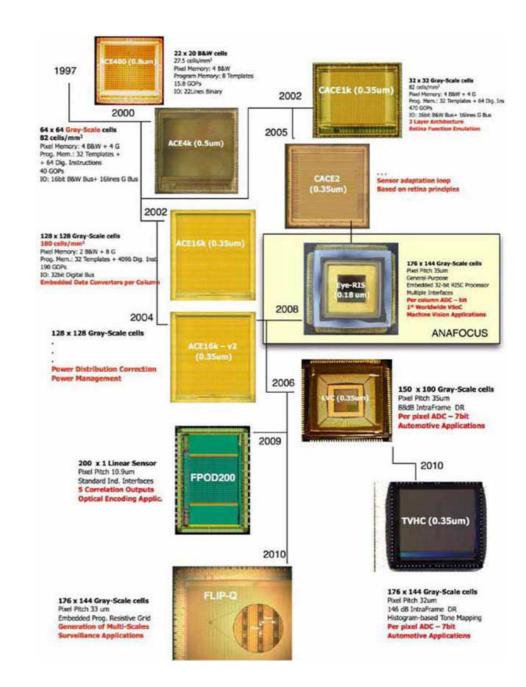

1995

國家國家主

#### Contact

Ángel Rodríguez Vázquez angel@imse-cnm.csic.es

Rocío del Río Fernández rocio@imse-cnm.csic.es

Research, development, and innovation regarding the implementation of high-performance mixed-signal interfaces, including front-end amplifiers, ADCs and DACs, in mainstream CMOS technological processes. Covered activities include:

- Exploration of novel architectural and circuital techniques for ADCs and DACs that are specially suited for low-voltage low-power operation in deep-submicron and nanometer CMOS processes.

- Development of top-down methodologies that support their optimized performance from the early design phases, including accurate behavioral modeling of mixed-signal circuital blocks.

- Exploration of reconfiguration strategies and programmability techniques at the architecture and circuit level for adaptive interface performance.

- Exploration of calibration techniques and architectures.

- Optimum chip implementation and verification. The areas of application include wireline, wireless and optoelectronic communications, sensor interfaces, and medical electronics.

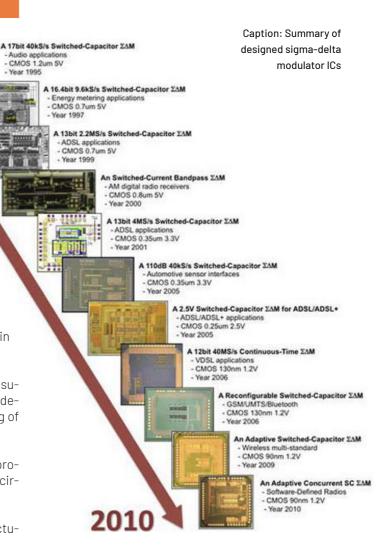

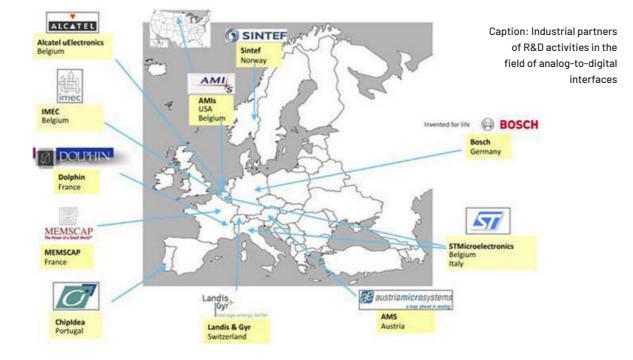

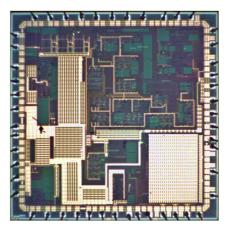

Expertise is supported by a long-term tradition (over 20 years) in the field of mixed-signal design, with special emphasis on sigma-delta, pipeline, ramp and SAR ADCs and several chips successfully transferred to industry. The accumulated know-how drives R&D, cooperation, and dissemination activities with both academia and world-leader industrial partners.

#### Keywords

ADCs; DACs; Mixed-Signal Interfaces; Nyquist; Sigma-Delta; Pipeline; SAR; Current-Steering; Design Methodologies; Behavioral Modeling; Performance Pptimization

#### Technology Transfer

Transference of a high-performance sigma-delta con-

verter designed by our research group to Alcatel Microelectronics and STMicroelectronics for its incorporation into the ADSL2+ modem chipset ST20190 Utopia for CPE applications (massive production in 2004).

#### **Research Highlights**

• J. Ruiz-Amaya, M. Delgado-Restituto and A. Rodriguez-Vazguez, "Device-Level Modeling and Synthesis of High-Performance Pipeline ADCs", Springer, 2011

• R. del Rio, F. Medeiro, B. Perez-Verdu, J.M. de la Rosa and A. Rodriguez-Vazguez, "CMOS Cascade Sigma-Delta Modulators for Sensors and Telecom: Error Analysis and Practical Design", Springer, 2006

• J. Ruiz-Amaya, J.M. de la Rosa, F.V. Fernandez, F. Medeiro, R. del Rio, B. Perez-Verdu and A. Rodriguez-Vazquez, "High-Level Synthesis of Switched-Capacitor, Switched-Current and Continuous-Time  $\Sigma\Delta$  Modulators using SIMULINK-Based Time-Domain Behavioral Mo-

dels", IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52 (9), pp. 1795-1810, 2005

• A. Rodriguez-Vazquez, F. Medeiro and E. Janssens (Eds.). "CMOS Telecom Data Converters", Springer, 2003

#### Key Research Projects & Contracts

SPIRIT: Secured Platform for Intelligent and Reconfigurable Voice and Data Terminals (MEDEA+ 2A101)

PI: Manuel Delgado Restituto

Funding Body: MEDEA+ (European public funding) 2006 - 2009

#### TAMES-2: Testability of Analog Macrocells Embedded into System-on-Chip (IST 2001-34283) PI: Belén Pérez Verdú Funding Body: European Union (European public fun-

ding) 2002 - 2004

# Design of Up-Stream and Down-Stream Data Converter for New Generation ADSL6

PI: Ángel Rodríguez Vázquez Funding Body: Alcatel Microelectronics (European private funding) 2001 - 2003

### Test and Design-for-Test of Analog, Mixed-Signals and RF (AMS-RF) Circuits

#### Contact

Diego Vázquez García

dgarcia@imse-cnm.csic.es

#### Gildas Léger

leger@imse-cnm.csic.es

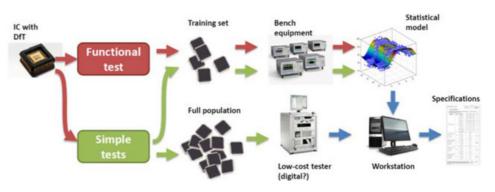

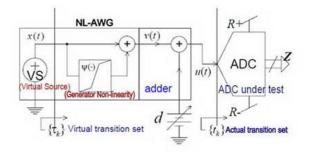

This research line gathers all the activities related to the development of test techniques. These can be lowcost functional approaches whose goal is the direct estimation of the specified performance. Other structural approaches (defect-oriented or indirect) make more use of Design-for-Testability features and rely on the consideration that the circuit is correct by design. As a result, they are more focused on the detection of spot defects or unexpectedly excessive parametric deviations. In both cases, embedded test techniques (commonly called Built-In Self-Test or BIST) are of particular interest to reduce test plan complexity, to enable the test of IP blocks with limited accessibility within a Systemon-Chip (SoC) or even to enable in-field testing (which increases system-level diagnosis capability). Our most recent research themes in this line are:

- On-line test and BIST for AMS-RF circuits.

- Characterization techniques for periodic signals and signal generation circuits for the embedded functional test of AMS circuits.

- Low-cost functional test techniques for Analog to Digital data converters.

- Machine-learning indirect test applied to AMS-RF circuits.

- Development of robust tests based on causal relationships.

#### Keywords

Mixed-Signal Integrated Circuits; Test; Testing; Design-for-Test (DfT); Built-In-Selft-Test (BIST); Machine-Learning

#### **Research Highlights**

◆ G. Leger and M. J. Barragan, "Brownian distance correlation-directed search: A fast feature selection technique for alternate test", Integration, the VLSI Journal, vol. 55, pp. 401–414, Sep 2016

◆ A.J. Gines E. Peralias, G. Leger, A. Rueda, G. Renaud, M.J. Barragan and S. Mir, "Linearity test of high-speed high-performance ADCs using a self-testable on-chip generator", IEEE European Test Symposium (ETS), Amsterdam, 2016

• M.J. Barragan and G. Leger, "A Procedure for Alternate Test Feature Design and Selection", IEEE Design & Test, vol. 32, no. 1, pp. 18–25, Feb 2015

M.J. Barragan, G. Leger, D. Vazquez and A. Rueda, "On-chip sinusoidal signal generation with harmonic cancelation for analog and mixed-signal BIST applications", Analog Integrated Circuits and Signal Processing, vol. 82, pp. 67-79, 2015

Best Special session award: M.J. Barragan, G. Leger,

F. Azais, R.D. Blanton, A. D. Singh and S. Sunter, "Special session: Hot topics: Statistical test methods," VLSI Test Symposium (VTS), Napa (USA), 2015

#### Key Research Projects & Contracts

IndieTEST: Indirect Test solutions for analog, mixed-signal and RF integrated systems (PICS CNRS) PI: Gildas Léger (CSIC) / Manuel Barragán (CNRS) Funding Body: CSIC & CNRS Jan 2017 - Dec 2019

n-PATETIC: New paradigms for testing mixed-signal integrated circuits (TEC2015-68448-R) PI: Adoración Rueda Rueda Funding Body: Min. de Economía y Competitividad Jan 2016 - Dec 2018

DANTE: Adapting Mixed-signal and RF ICs Design and Test to Process and Evironment Variability (TEC2011-28302)

PI: Adoración Rueda Rueda Funding Body: Min. de Ciencia e Innovación Jan 2012 - Dec 2014

# ACATEX: Self-calibration and self-test of analog, mixed-signal and radio frecuency circuits (P09-TIC-5386)

PI: Adoración Rueda Rueda Funding Body: Junta de Andalucía - Proyectos de Excelencia. Mar 2010 - Feb 2014

#### TOETS: Towards One European Test Solution

PI: José L. Huertas Díaz Funding Body: CE: CATRENE European Program -CT302. Dec 2009 - Nov 2011

Caption: Statistical post processing for Alternate Test. From a completely characterized subset of circuits, a machine-learning algorithm extracts the non-linear and multi-dimensional relations between simple signatures and specifications. This model is further used to test the rest of circuits with the simple signatures only.

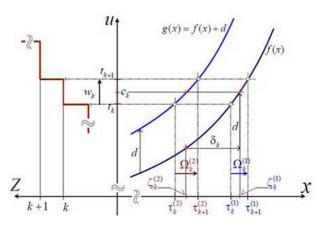

Measurement method ] Caption: Measurement method for ADCs based on double-histogram. From the histograms (output code density) obtained for a non-linear monotonous input signal and its replica with an additive offset, the INL of a highresolution ADC can be retrieved at low cost.

#### Modeling, Design and Synthesis Techniques of Analog, Mixed-Signal, RF and Heterog neous Circuits and Systems

#### Contact

#### Francisco V. Fernández Fernández pacov@imse-cnm.csic.es

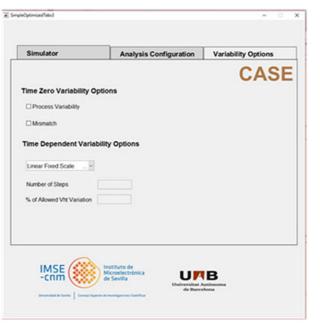

The general objective of this research line is to develop new modeling, design and synthesis strategies for analog, mixed-signal, radio-frequency (RF) and heterogeneous integrated circuits and systems, aiming at better performances, smaller design and fabrication cost and smaller power consumption. This also involves dealing with the increasing variability of modern technologies.

More specifically, the work includes activities in different aspects of the circuit design flow, as well as their exploitation in industrial-class designs:

- Pareto-based behavioral modeling with support to multiple hierarchical design flows.

- Layout-aware synthesis methodologies for analog/RF circuits.

- Electromagnetic-simulation-based performance modeling of passive devices for RF circuit design.

- Variability-aware design techniques.

- Development and exploitation of emerging design methodologies: bottom-up techniques, hybrid techniques and competitive strategies.

- Simulation techniques for time-zero and time-dependent variability.

#### Keywords

Systematic Design Methodologies; Single-Objective and Multi-Objective Optimization; Reconfigurable Design; Layout-Aware Design; Variability-Aware Design; Aging Simulation

#### **Research Highlights**

◆ F. Passos, E. Roca, J. Sieiro, R. Castro-Lopez and F.V. Fernandez, "An Efficient Transformer Modeling Approach for mm-Wave Circuit Design", AEU - International Journal of Electronics and Communications, vol. 128, article 153496, 2021

◆ F. Passos, E. Roca, R. Martins, N. Lourenço, S. Ahyoune, J. Sieiro, R. Castro-Lopez, N. Horta and F. V. Fernandez, "Ready-to-Fabricate RF Circuit Synthesis using a Layout- and Variability-Aware Optimization-based Methodology", IEEE Access, vol. 8, pp. 51601-51609, 2020

| <ul> <li>SiDe-O   Surrogate Inductor Design and Optimization</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inductor Optimization                                                   | and the second sec |

| Asymetric Dol anductor (P1 ten F2 tel: Single-objective)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Single-Objective Optimization Optimization                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| manna bash factor 🔒 👘 🗛                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Money Deared Macania Region of Optimization                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 246 21 81 Objectives Aut 1 Parts                                        | SIDe-O ToolBox                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| pressure advocute                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10 100 Input Surfayments                                                | *** Hell brown have been at brown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Obtained Inductor                                                       | The first have been been been been been been been be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| a Degrey agent Destgrey                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2 200 12.0 200.2                                                        | - Rectange System, N. R.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Industrance Quality Factor                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A MOVE TRADE Multi-objective                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Multi-Objective Optimization Optimization                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Warmen (if and Inductance                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Hang<br>Pasania<br>Pasania                                              | w/w/res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Sine Optimization Star Optimization                                     | The last has been been been been been been been bee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Norther of Norther of preventions Industrial                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Message                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Board and REACHIE                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |