## **EU Projects**

NABAB: Nano Computing Building Blocks with Acquired Behaviour. FP7-216777

CAVIAR: Convolution Address-Event-Representation (AER) Vision Architecture for Real-Time. FP5-IST-2001-34124

**PNEUMA** Plasticity in Neural Memristive Architectures. PRI-PIMCHI-2011-0768.

**NEURAM3**: NEUral computing aRchitectures Advanced in Monolithic **3D-VLSI** nanotechnologies. H2020: ICT 25-2015-687299

HBP: The Human Brain Project. H2020-HBP-604102

ECOMODE: Event-driven compressive vision for multimodal interaction with mobile devices. H2020-ICT-2014-1-644096

CONSEJO SUPERIOR DE INVESTIGACIONES CIENTÍFICAS

#### References

(Serrano 2013a) T. Serrano-Gotarredona et al., "A 128x128 1.5% Contrast Sensitivity 0.9% FPN 3us Latency 4mW Asynchronous Frame-Free Dynamic Vision Sensor Using Transimpedance Amplifiers," IEEE JSSC, vol.48, No. 3, 2013

(Leñero 2011) J. A. Leñero-Bardallo, et al., "A 3.6us Asynchronous Frame-Free Event-Driven Dynamic-Vision-Sensor," IEEE JSSC, vol. 46, No. 6, 2011

(Leñero 2010) J. A. Leñero-Bardallo, et al., "A 5-Decade Dynamic Range Ambient-Light-Independent Calibrated Signed-Spatial-Contrast AER Retina with 0.1ms Latency and Optional Time-to-First-Spike Mode," IEEE TCASI, vol. 57, No. 10, 2010

(Costas-Santos 2007) J. Costas-Santos et al., "A Spatial Contrast Retina with On-chip Calibration for Neuromorphic Spike-Based AER Vision Systems," IEEE TCASI, vol. 54, No. 7, 2007

(Camuñas 2012) L. Camuñas-Mesa et al., "An Event-Driven Multi-Kernel Convolution Processor Module for Event-Driven Vision Sensors," IEEE JSSC, vol. 47, No. 2,. 2012

(Camuñas 2011) L. Camuñas-Mesa et al., "A 32x32 Pixel Convolution Processor Chip for Address Event Vision Sensors with 155ns Event Latency and 20Meps Throughput," IEEE TCASI, vol. 58, No. 4, 2011

(Serrano 2006) R. Serrano-Gotarredona et al. "A Neuromorphic Cortical-Layer Microchip for Spike-Based Event Processing Vision Systems," IEEE TCASI, vol. 53, No. 12, 2006.

(Serrano 2008) R. Serrano-Gotarredona, et al., "On Real-Time AER 2D Convolutions Hardware for Neuromorphic Spike Based Cortical Processing," IEEE TNN, vol. 19, No. 7, 2008.

(Zamarreño 2013) C. Zamarreño-Ramos et al., "Multi-Casting Mesh AER: A Scalable Assembly Approach for Reconfigurable Neuromorphic Structured AER Systems. Application to ConvNets," IEEE TBIOCAS, vol. 7, No. 1, 2013

(Camuñas18) L. Camuñas-Mesa et al., "A Configurable Event-Driven Convolutional Node with Rate Saturation Mechanism for Modular ConvNet Systems Implementation," Frontiers in Neuromorphic Engineering. doi: 10.3389/fnins.2018.00063

(Serrano2013b)T. Serrano-Gotarredona, et al. "STDP and STDP Variations with Memristors for Spiking Neuromorphic Learning Systems," Frontiers in Neuromorphic Engineering, doi: 10.3389/fnins.2013.00002

# **Neuromorphic Systems Group**

## Instituto de Microel Spanish Researc

#### University o

Since its coordination of the E CAVIAR project (www.ims cnm.csic.es/caviar), the IMS Neuromorphic group develo sensory and processing microchi that mimic sensing and processing biological beings. It also develop multi-chip and hybrid chip-FPG systems to scale up to highe complexity systems. The group als works on algorithms and sensor processing for spiking informatio sensing, coding and processing Chips use mixed signal, low curren and/or low power, circuit technique. well as high spee as communication techniques. Th group uses mixed or digital CMC technologies, as well as application projections exploiting emerger nanoscale technologies or ne like devices memristo

#### Contact

Bernabé Linares-Barranco http://www2.imse-cnm.csic.es/~bernabe bernabe@imse-cnm.csic.es 34 954 446643

Teresa Serrano-Gotarredona http://www2.imse-cnm.csic.es/~terese terese@imse-cnm.csic.es 34 954 446644

| ectrónica de Sevilla |                                                |

|----------------------|------------------------------------------------|

| ch C                 | ouncil- CSIC                                   |

| ofSev                | ville - US                                     |

| U                    |                                                |

| e- R<br>E            | lesearch Lines:                                |

| ps 🗸                 | Bioinspired Vision Sensors                     |

| ps √                 | Spiking Convolution Chips                      |

| in<br>os<br>∕A       | Multi-chip and Hybrid Chip-<br>FPGA processors |

|                      | Sensory-Processing on the SpiNnaker platform   |

|                      | Spiking Information<br>Processing              |

| g. √                 | Spike Learning                                 |

| s,                   | Low-power, low-current circuits                |

| ed ✓                 | High-speed communication                       |

| ne<br>S ✓<br>on      | Neuromorphic systems with memristors           |

| nt<br>w<br>rs        | SE-DVS                                         |

|                      |                                                |

Instituto de Microelectro de Sevilla

### Bioinspired Vision Sensors

Event-driven retinas do not produce sequences of still frames, as conventional video cameras do. Instead, each pixel senses light and computes a given property (spatial contrast, temporal change) continuously in time. Whenever this property exceeds a given threshold, the pixel sends out a spike coded as an address event (which usually consists of the pixel x,y coordinate and the sign of the threshold), which is written onto one (or more) high speed bus with asynchronous handshaking. This way, sensors produce continuous event flows, and subsequent processors process them event by event.

The group has developed a catalog of spiking vision sensors:

- ✓ 128x128 Temporal Contrast Retina with Improved Contrast Sensitivity and Reduced FPN (Serrano 2013)

- ✓ 128x128 Temporal Contrast Retina with Improved Contrast Sensitivity (<u>Leñero</u> <u>2011</u>)

- ✓ 32x32 Spatial Contrast Retina with Onchip Calibration and Time-to-first Spike Mode (Leñero 2010)

- 32x32 Spatial Contrast Retina with Onchip Calibration (Costas-Santos 2007)

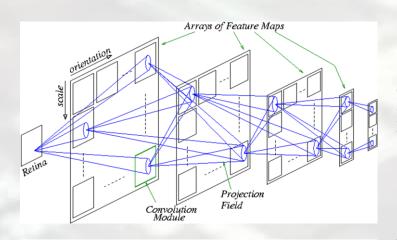

## Spiking ConvNets

Convolutional Neural Networks (ConvNets) are bioinspired hierarchical architectures that perform complex recognition tasks. They are commonly used in deep networks artificial intelligence vision systems. However, they do computation and object recognition on still frames. The connection weights are trained using conventional backpropagation algorithms on sets of static training images. The IMSE Neuromorphic group has done research on algorithms and hardware for implementing third generation spiking neural networks using spiking ConvNets.

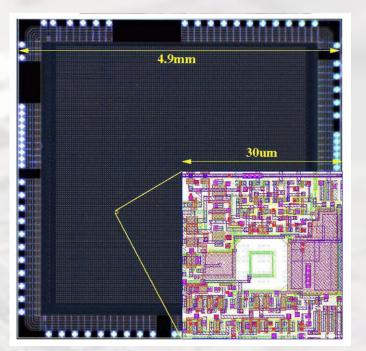

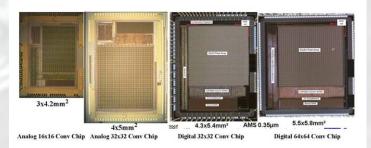

They have a catalog on fully programmable weights and modularly interconnectable Spiking Convolution microchips:

- ✓ 64x64 AER Convolution Chip with Digital Pixel Operation, Multikernel Capability, Kernels with up to 32x32 weights, and 175ns latency. (Camuñas 2012)

- ✓ 32x32 AER Convolution Chip with Digital Pixel Operation, Kernel up to 32x32 weights, and 155ns latency. (Camuñas 2011)

- ✓ 32x32 AER Convolution Chip with Analog Pixel Operation and Kernel up to 32x32 weights (Serrano 2006)

- ✓ 16x16 AER Convolution Chip with Analog Pixel Operation Kernel up to 16x16 weights (<u>Serrano 2008</u>)

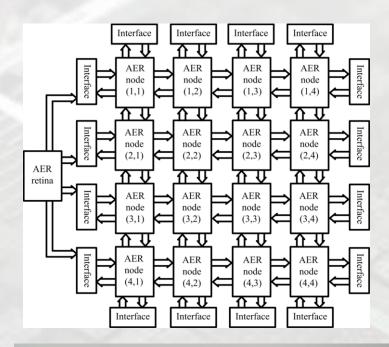

The group has also developed programmable modular Spiking ConvNets using routers and convolutional modules implemented on FPGAs

- ✓ Reconfigurable 2D array of AER Convolution Processors on a Virtex6 FPGA (Zamarreño 2013, Camuñas18).

- ✓ Node Board: special purpose board to be modularly assembled in a 2-D grid fashion to build large scale spiking convolution networks. Each node contains a 2-D grid of convolution modules inside the same FPGA XC6SLX150T Spartan6 and four SATA connectors to assemble the boards in a 2D-mesh fashion. Additionally, the board contains two parallel AER connectors to link the FPGA with external AER components (AER sensors, AER convolution chips, etc...)

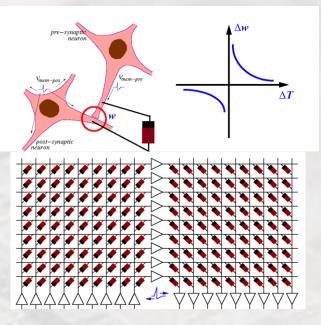

#### Memristive NCSs

The group has proposed and designed Neuromorphic Computing Systems (NCSs) based on hybrid combination of CMOS spiking neurons and dense memristive synaptic arrays. The memristor devices when stimulated with different waveforms of pre and post spikes undergo a variety of bioinspired Spike-Time-Dependent-Plasticity (STDP) rules . (Serrano2013b). Memristive NCS are promising canditates to implement very large scale low power self-learning systems.