AER Vision Processors

![]() CONVOLUTION NETWORKS ON FPGA

CONVOLUTION NETWORKS ON FPGA

- Reconfigurable 2D array of AER Convolution Processors on a Virtex6 FPGA (Zamarreño 2013).

A system of 64 Gabor filters AER modules with reconfigurable interconnection, each with 64x64 pixels and kernels of size 11x11 has been assembled.

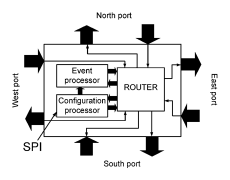

AER convolution processors are interconnected in a 2D mesh fashion as show in the right figure below.

Each AER module has 4 routing channels and contains an AER convolution processor plus a configurable router that sets the network connectivity by sending each incoming event to the local processor or directing it through the corresponding channel towards its destination processor.

- Node Board

A special purpose board named ‘Node Board’ has been designed intended to be assembled in a 2-D grid fashion to build large convolution networks each node containing

a 2-D grid of convolution modules inside the same FPGA. The node board contains a XC6SLX150T Spartan6 FPGA and four SATA connectors to assemble the boards in a 2D-mesh fashion. The inter board data communication is implemented using the FPGA Rocket I/O GTP transceivers. Additionally, the board contains two parallel AER connectors to link the FPGA with external AER components (AER sensors, AER convolution chips, etc…)

![]() CONVOLUTION CHIPS

CONVOLUTION CHIPS

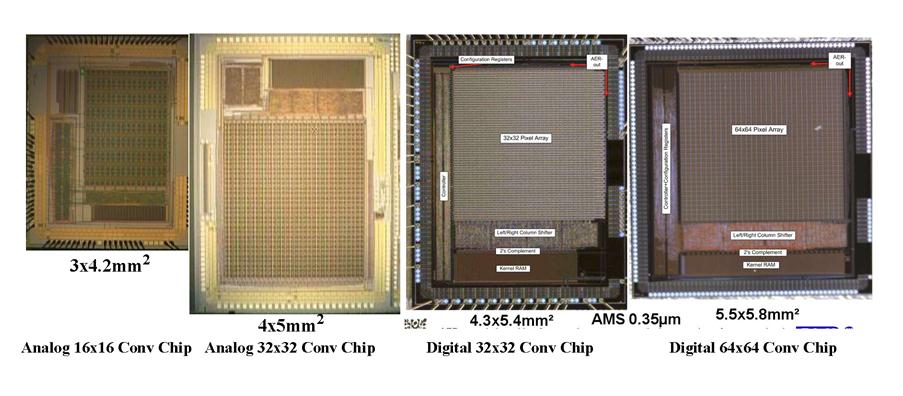

- 64x64 AER Convolution Chip with Digital Pixel Operation, Multikernel Capability, Programmable Kernels with up to 32x32 weights (if only 1 kernel is programmed) with no shape restriction and 4 bit resolution for weights and 6 bit resolution for neuron state and 175ns latency. (Camuñas 2012)

- 32x32 AER Convolution Chip with Digital Pixel Operation and Programmable Kernel up to 32x32 weights with no shape restriction and 6 bit resolution for weights and 18 bit resolution for neuron state and 155ns latency. (Camuñas 2011)

- 32x32 AER Convolution Chip with Analog Pixel Operation and Programmable Kernel up to 32x32 weights with no shape restriction and 1ms latency (Serrano 2006)

- 16x16 AER Convolution Chip with Analog Pixel Operation and Programmable Kernel up to 16x16 weights with no shape restriction (Serrano 2008)