Hardware Security

The development of IoT in the near future faces numerous technological challenges that need to be addressed, such as power/energy efficiency, reliability, security, and cost. Advanced CMOS technologies are potential candidates for solutions in the short term to those challenges, whereas beyond-CMOS devices are the answer for solutions in the long term. All these technologies are plagued with both time-zero and time-dependent variability effects. From a reliability point of view, design strategies and methodologies are required to deal with the mitigation or tolerance to variability effects. But from an exploitation perspective, variability can be regarded as an advantage rather than as a problem, e.g. in the hardware security field.

This research line focusses in the development of new and robust Physical Unclonable Functions and lightweight cryptographic solutions combining the experience of researchers in reliability characterization and reliability-aware design in CMOS technology and low-power circuit design in beyond-CMOS technologies. More specifically, the work includes activities in the following design areas:

P. Saraza-Canflanca, H. Carrasco-Lopez, A. Santana-Andreo, P. Brox, R. Castro-Lopez, E. Roca and F.V. Fernandez, "Improving the reliability of SRAM-based PUFs under varying operation conditions and aging degradation", Microelectronics Reliability, vol. 118, article 114049, 2021. » doi

P. Saraza-Canflanca, J. Martin-Martinez, R. Castro-Lopez, E. Roca, R. Rodriguez, F.V. Fernández and M. Nafria, "Statistical characterization of time-dependent variability defects using the máximum current fluctuation", IEEE Transactions on Electron Devices, vol. 68, no. 8, pp 4039-4044, 2021 » doi

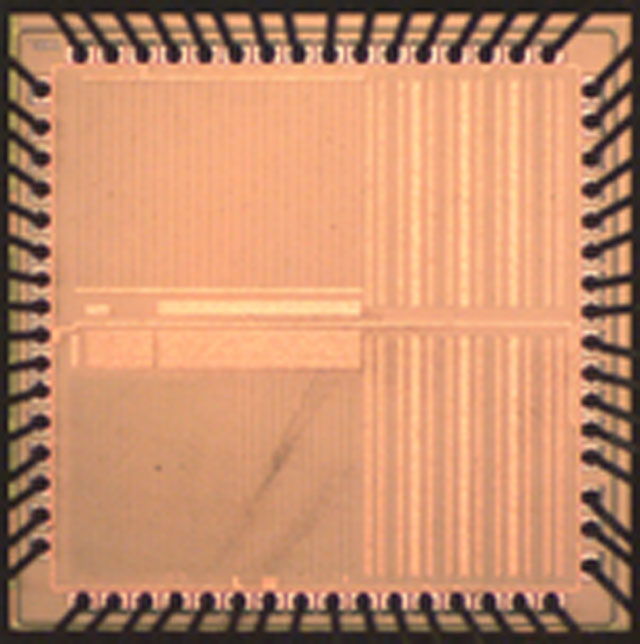

J. Díaz-Fortuny, P. Saraza-Canflanca, R. Castro-Lopez, E. Roca, J. Martin-Martinez, R. Rodriguez, F.V. Fernández and M. Nafria, "Flexible Setup for the Measurement of CMOS Time-Dependent Variability with Array-Based Integrated Circuits", IEEE Transactions on Instrumentation and Measurement, vol. 69, no. 2, pp 853-864, 2020 » doi

I.M. Delgado-Lozano, E.Tena-Sánchez, J. Núñez and A. Acosta, "Design and analysis of secure emerging crypto-hardware using HyperFET devices", IEEE Transactions on Emerging Topics in Computing, vol. 9, no. 2, pp 787-796, 2020 » doi

J. Diaz-Fortuny, J. Martin-Martinez, R. Rodriguez, R. Castro-Lopez, E. Roca, X. Aragonés, E. Barajas, D. Mateo, F.V. Fernandez and M. Nafria, "A Versatile CMOS Transistor Array IC for the Statistical Characterization of Time-Zero Variability, RTN, BTI and HCI", IEEE Journal of Solid-State Circuits, vol. 54, no. 2, pp 476-488, 2019 » doi

VIGILANT: The Variability Challenge in Nano-CMOS - SUBPROJECT MITIGATION (PID2019-103869RB-C31)

PI: Francisco V. Fernández Fernández / Rafael Castro López

Funding Body: Min. de Ciencia, Innovación y Universidades

Jun 2020 - May 2023

TOGETHER: Towards Trusted Low-Power Things: Devices, Circuits and Architectures (TEC2016-75151-C3-3-R)

PI: Francisco V. Fernández Fernández / Rafael Castro López

Funding Body: Min. de Economía, Industria y Competitividad

Jan 2017 - Jun 2021